§4.1 概述

§4.2 常用触发器介绍

§4.3 触发器逻辑功能的转换

§4.4 触发器的应用举例

以下内容为正文:

§4.1 概述

时序电路现时的输出不仅取决于现时的输入,还取决于电路原来的状态。也就是说时序电路能记住电路的原有状态,这种忆功能是靠“双稳态触发器”(flip-flop)来实现的,所以在讨论具体时序电路之前,要先介绍触发器。

记忆功能的实现

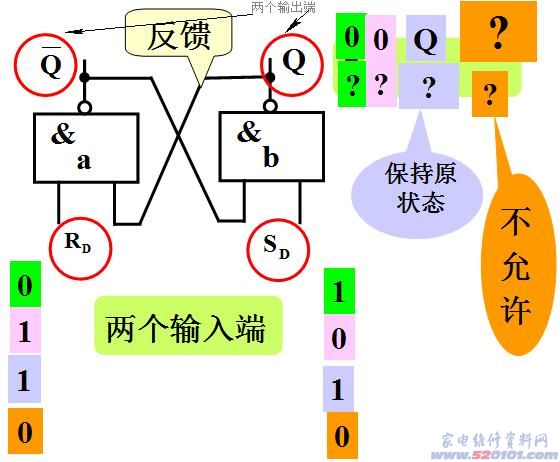

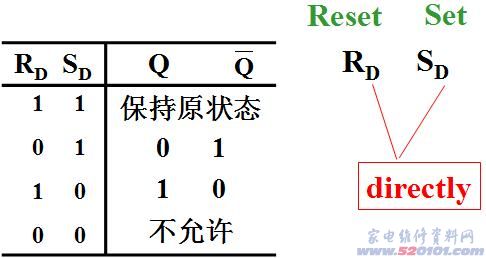

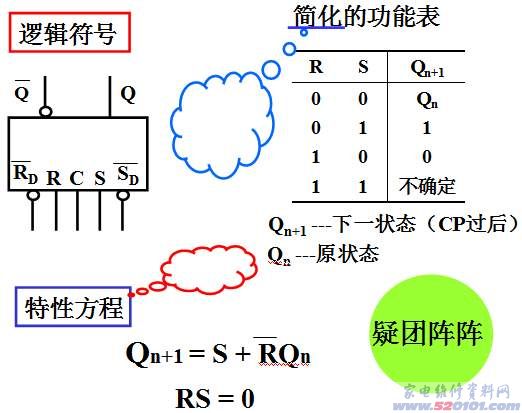

基本RS触发器的功能表

小结

1.基本 RS触发器是双稳态器件,只要令RD=SD=1,触发器即保持原态。稳态情况下,两输出互补。一般定义Q为触发器的状态。

2. 在控制端加入负脉冲,可以使触发器状态变化。SD端加入负脉冲,使Q=1,SD称为“置位”或“置1”端。RD端加入负脉冲,使Q=0,RD称为“复位”或“清0”端。

§ 4.2 常用触发器介绍

1 基本 RS触发器

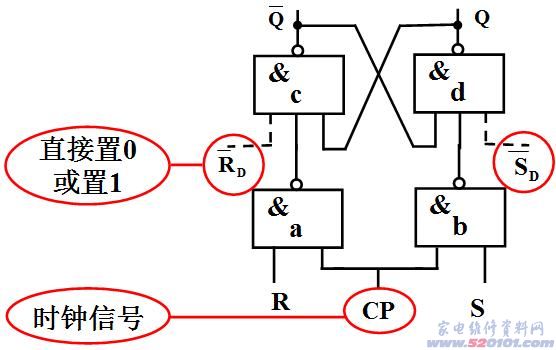

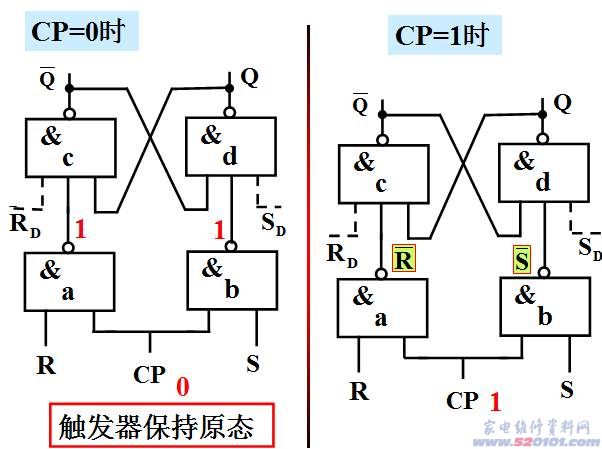

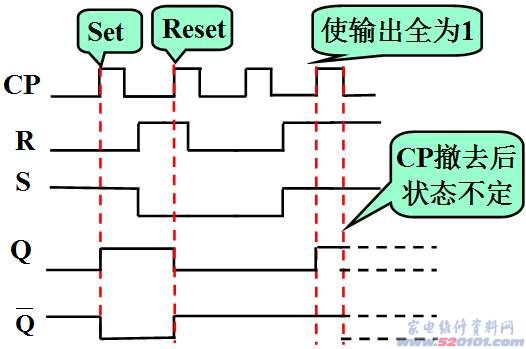

2 同步 RS触发器(钟控RS,可控RS)

对R,S控制信号有要求?

注意

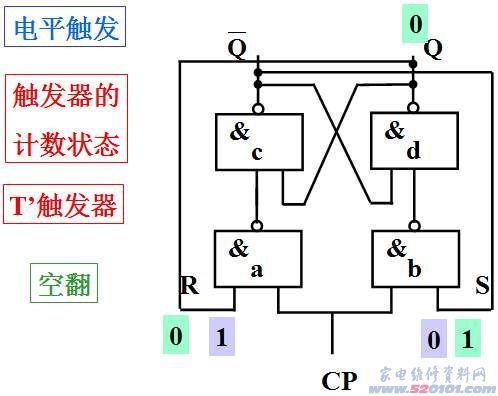

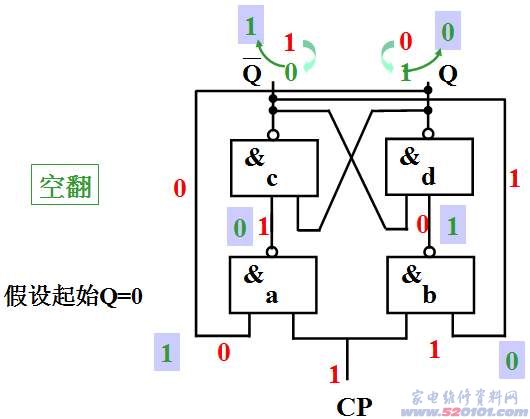

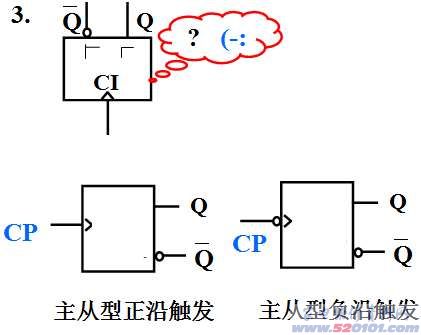

电平触发的触发器在接成计数状态时会产生空翻现象( 即CP=1期间,输出状态翻转若干次,因而不能正常计数。) 。

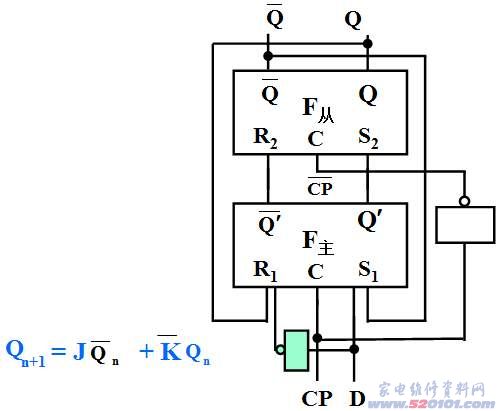

克服空翻现象的方法之一是: 采用主从触发方式。

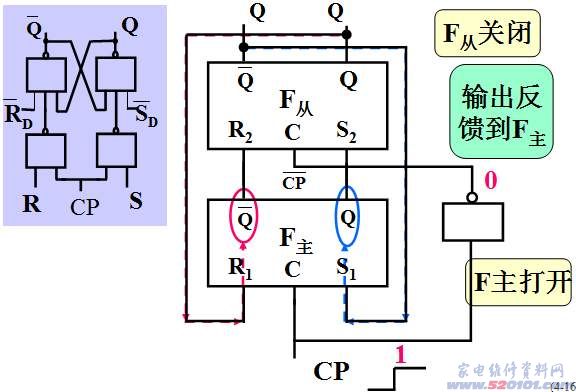

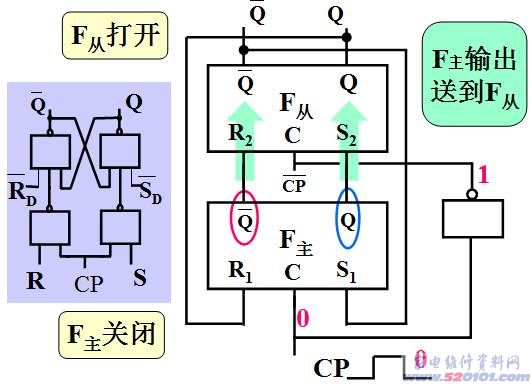

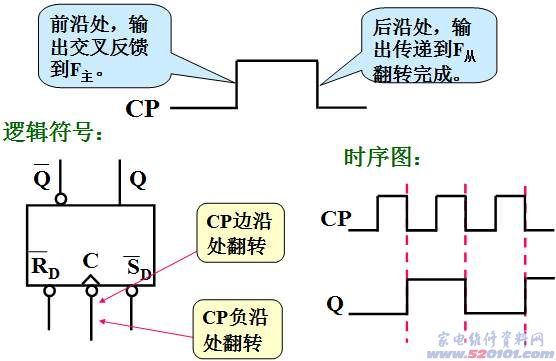

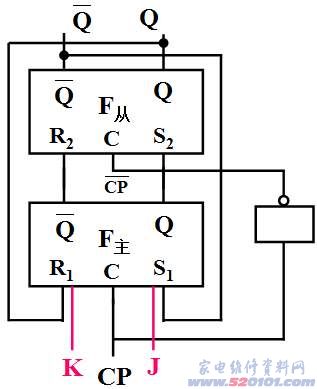

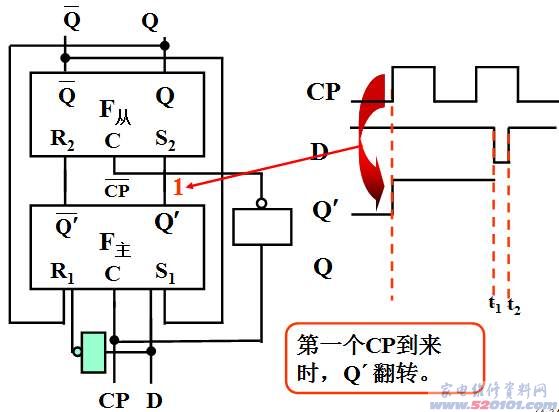

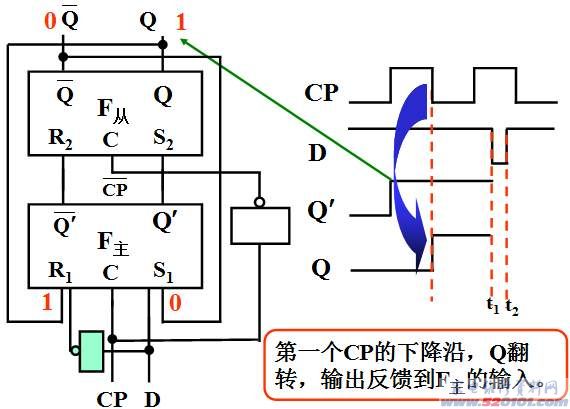

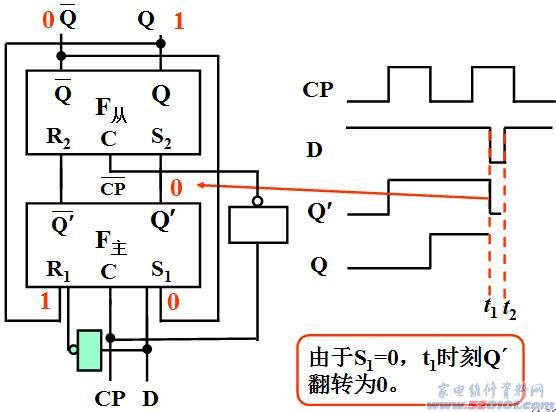

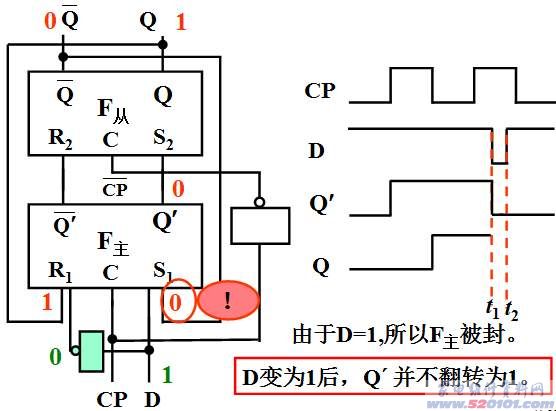

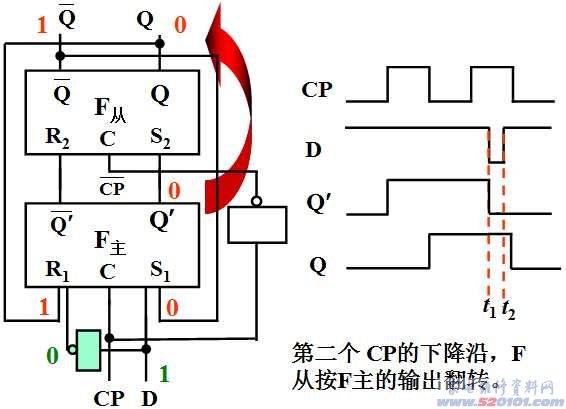

上图主从触发方式T' 触发器的电路结构

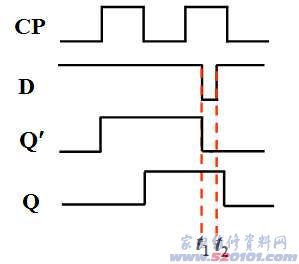

下图主从触发方式T' 触发器的工作原理

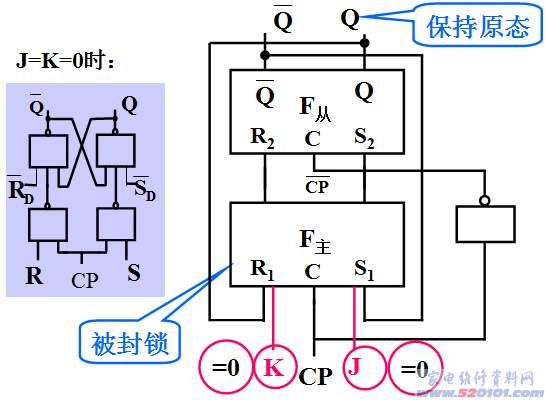

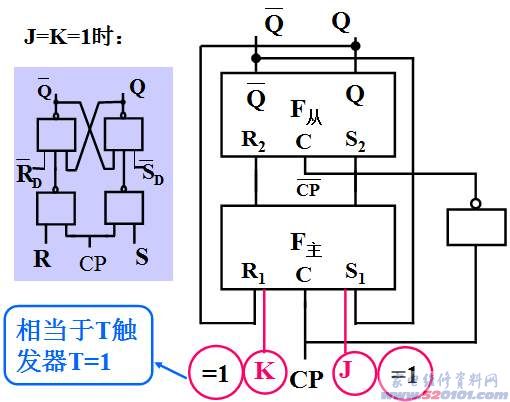

综合上述分析,主从触发器来一个CP 只能翻转一次。

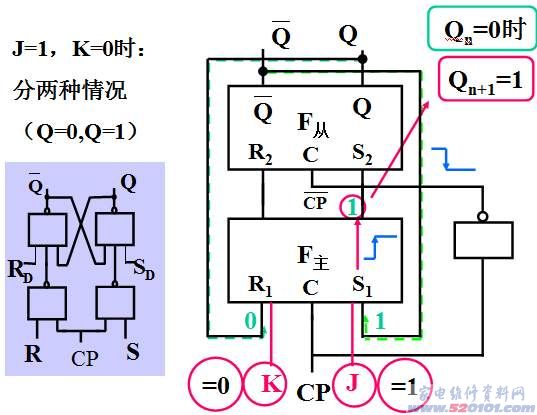

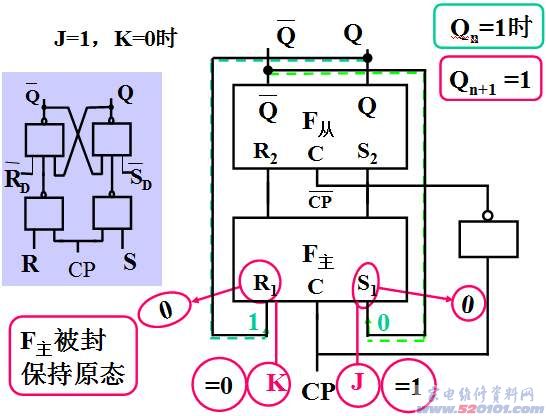

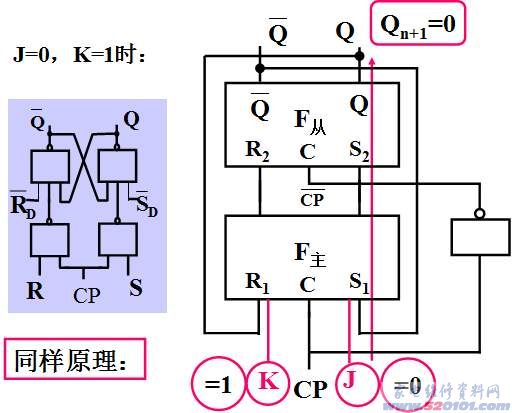

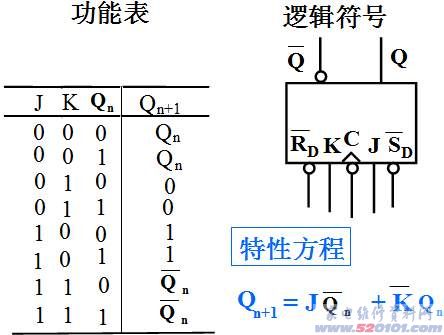

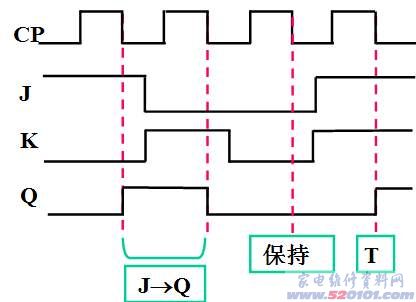

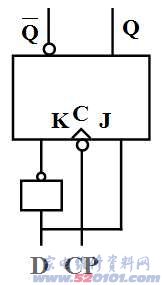

4. JK触发器

JK触发器的功能最完善,有两个控制端J、K。

时序图

小结:

从逻辑功能来看:

1. 基本RS触发器

2. 同步RS触发器

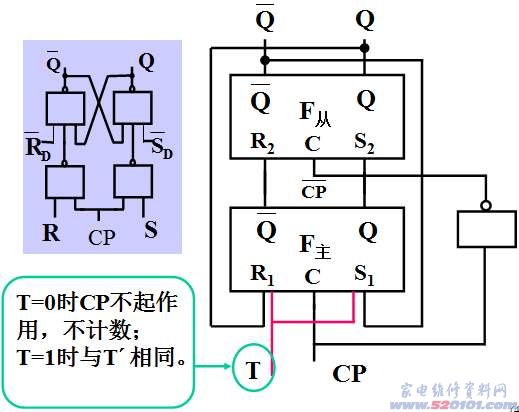

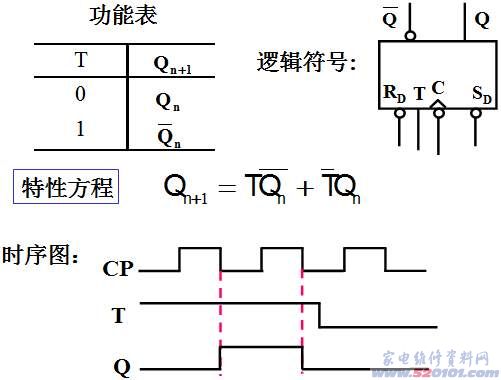

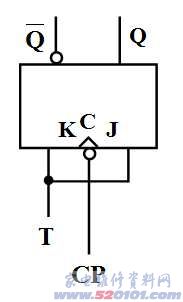

3. T’和T触发器

4. JK触发器

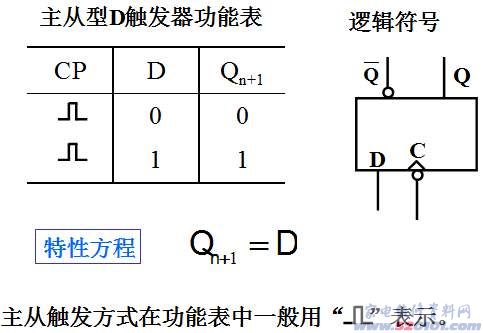

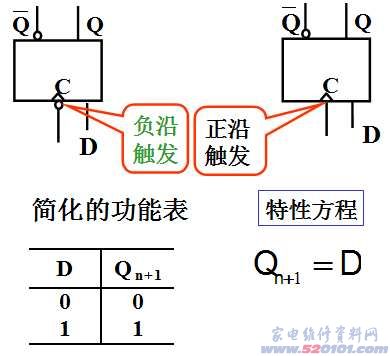

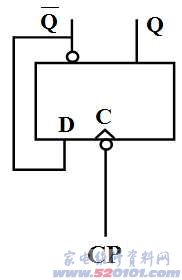

5. D触发器

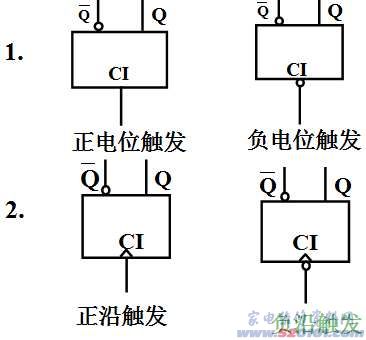

从电路结构及触发方式来看:

以主从触发的D触发器为例:

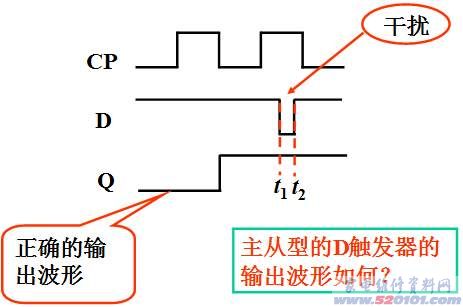

假设在CP=1期间 D有一干扰

由于D在CP=1期间有干扰,便产生了错误的输出。因此,主从触发器不允许在CP=1期间有干扰,否则可能产生误动作。

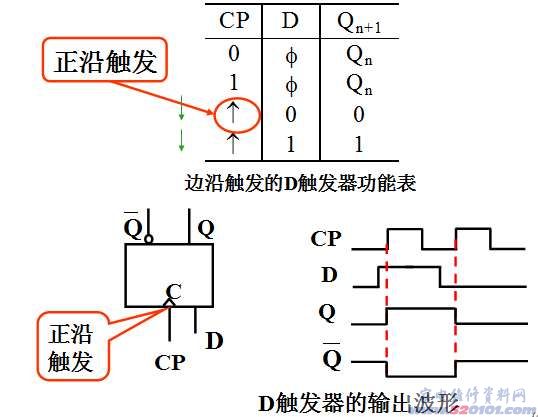

边沿触发方式

为了免除CP=1期间输入控制电平不许改变的限制,采用边沿触发方式。其特点是:触发器只在时钟跳变时刻发生翻转,而在CP=1或CP=0期间,控制端的任何变化都不影响输出。

如果翻转发生在上升沿就叫“上升沿触发”或“正边沿触发”。如果翻转发生在下降沿就叫“下降沿触发”或“负边缘触发”。下面以边缘触发的D触发器为例讲解。

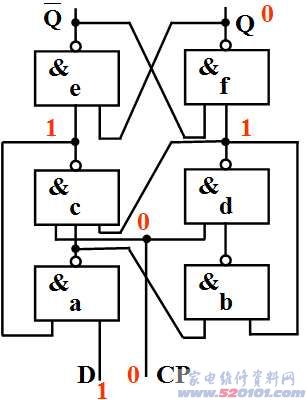

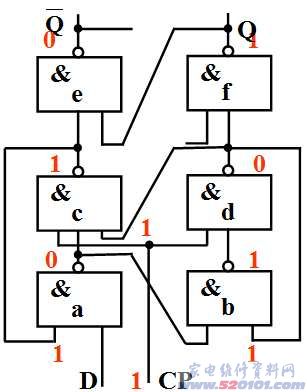

设原态Q=0,并设D=1。

CP=0期间:

(1) c 、d被锁,c、d的输出均为1。

输出保持原状态

不变

CP=0期间:

(2) c=1 、d=1反馈到a、b的输入,a、b输出为0、1。

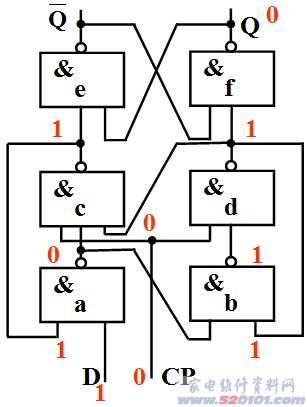

CP正沿过后:

d=0将c封锁,并使b=1,维持d=0。

因此以后CP=1期间D的变化不影响输出。

* 在应用触发器时,要特别注意触发形式,否则很容易造成整个数字系统工作不正常。

** 边沿触发抗干扰能力强,且不存在空翻,应用较广泛。

§4.4 应用举例

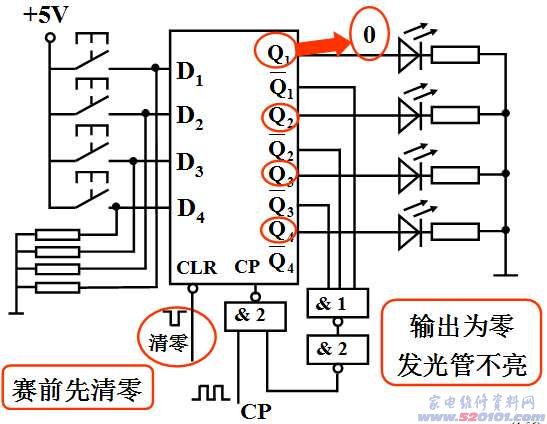

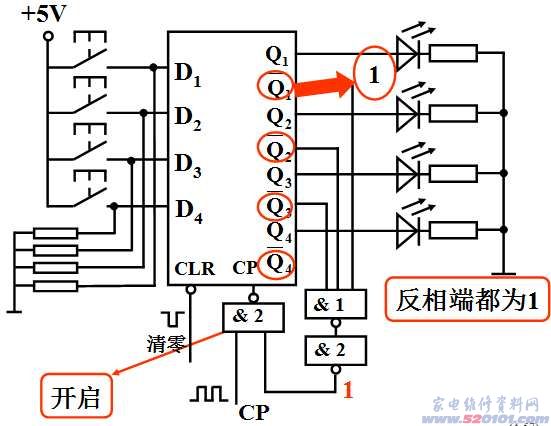

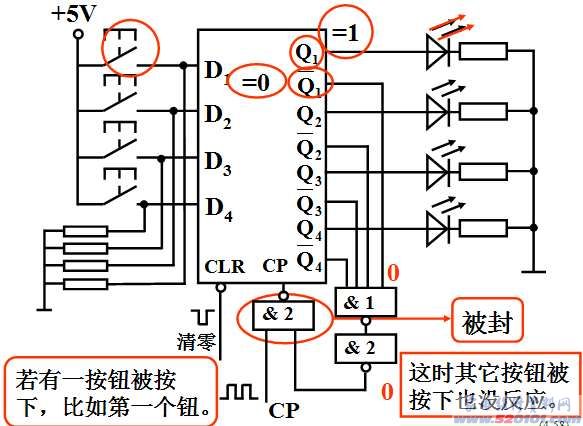

例:四人抢答电路。四人参加比赛,每人一个按钮,其中一人按下按钮后,相应的指示灯亮。并且,其它钮再按下,不起作用。

电路的核心是74LS175四D触发器。它的内部包含了四个D触发器,各输入、输出以字头相区别,管脚图见下页。

本课节结束,未完 待续....

网友评论