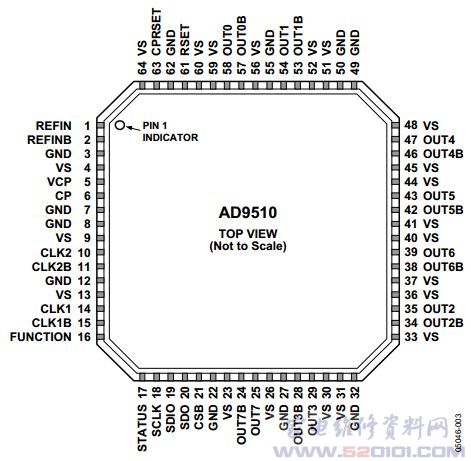

概述:AD9510采用四面64脚封装。

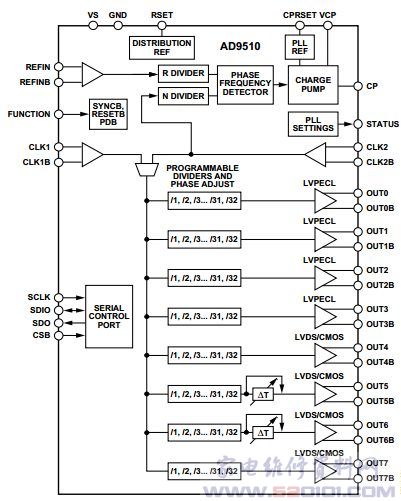

AD9510提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。4路独立的LVPECL时钟输出和4路LVDS时钟输出工作频率分别为1.2GHz和800MHz。可选的CMOS时钟输出工作频率为250MHz。

PLL部分由可编程参考分频器(R)、低噪声鉴频鉴相器(PFD)、精密电荷泵(CP)和可编程反馈分频器(N)组成。将外部VCXO或VCO连接到CLK2和CLK2B引脚时,最高达1.6GHz的PLL输出频率可以与输入参考REFIN同步。

时钟分配部分提供LVPECL输出和可编程为LVDS或CMOS的输出。每路输出都有一个可编程分频器,可以旁路该分频器或者设置最高32的整数分频比。

网友评论