DC 规格包括整个温度范围内的 ±0.3LSB INL (典型值)、±0.1LSB DNL (典型值) 和无漏失码。转换噪声很低,仅为 0.3LSBRMS。

数字输出为串行 LVDS,旨在最大限度地减少数据线的数目。每个通道一次输出两个位 ("双线道" 模式) 或一个位 ("单线道" 模式)。LVDS 驱动器具有可任选的内部终端和可调输出电平,以确保干净的信号完整性。

可以利用一个正弦波、PECL、LVDS、TTL 或 CMOS 输入对 ENC+ 和 ENC¯ 输入进行差分或单端驱动。一个内部时钟占空比稳定器在全速和多种时钟占空比条件下实现了高性能。

一、功能和特性

4通道同步采样ADC

71dBSNR

90dBSFDR

低功率:306mW/198mW/160mW(总值)

77mW/50mW/40mW(每通道)

串行LVDS输出:每通道1位或2位

可选输入范围:1VP-P至2VP-P

800MHz满功率带宽采样及保持

停机和打盹模式

用于配置的串行SPI端口

引脚兼容的14位和12位器件版本

二、LTC2171-12引脚功能

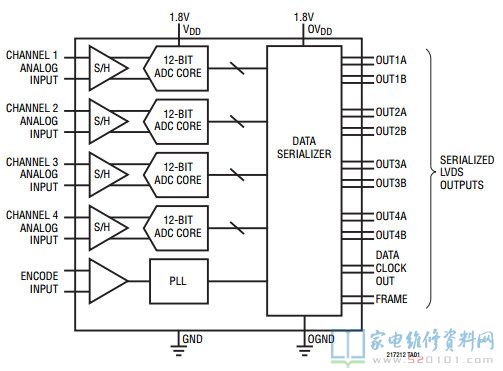

三、LTC2171-12内部方框图

四、LTC2171-12典型应用电路

网友评论