概述:MST9883(UN700 衍生型号MST9883KST-110、MST9883B)是晨星半导体公司生产的一款专为平板显示模拟前端接口设计的模数转换集成电路。它为单一3.3V供电电压,它内置三通道8位110MHz采样频率AD转换器、同步处理器及时钟发生器、I2C主机接口等功能模块,数字视频输出接口支持4:4:4 RGB/YUV模式输出或4:2:2 YUV标准的数字视频格式编码输出。

四、MST9883几个特殊功能引脚说明

①HSOUT((66)脚)行同步信号输出:行同步信号用来确定水平方向每行图像的显示起点,它由前端(30)脚输入的行同步信号直通得到,或者由集成电路内部同步信号处理电路,从复合同步信号或G(绿基色)信号中,经同步分离电路分离产生,其输出极性由I2C总线控制的寄存器控制。

②VSOUT((64)脚)场同步信号输出:场同步信号用来确定垂直方向每场(帧)图像的显示起点,同样它也由前端(31)脚输入的场同步信号直通得到,或者由集成电路内部同步信号处理电路,从复合同步信号或G信号中,经场同步分离电路产生,其输出极性由I2C总线的寄存器控制。

(3)DCK((67)脚)数据时钟信号输出:DCK是数据信号采样时钟信号输出,它由输入的行同步信号控制集成电路内的锁相环压控振荡器产生,它能保证每行起点的取样时钟相位准确,采样时钟信号的相位稳定性,直接影响显示画面图像的稳定性。

(4)I2C总线控制,SDA((57)脚)、SCL((56)脚)、AO((55)脚):12C总线的控制包括:串行数据线(SDA)、串行时钟线(SCL)、串行地址线输入(AO),它们共同完成I2C总线的控制功能。

⑤R[O~7]((70)~(77)脚):8比特红基色信号并行输出。

⑥G[0~7](②~⑨脚):8比特绿基色信号并行输出。

⑦B[0~7]((12)~(19)脚):8比特蓝基色信号并行输出。

以上三项是R、G、B三基色数据信号并行输出,最高位为MSB,最低位为LSB,从像素的采样到信号输出的延时是固定的。当采样时间随相位调整器改变时,输出信号时序、时钟、数据信号等与行同步信号输出也会改变,因此时序信号的稳定性,即采样时钟信号的稳定性与显示图像的稳定性有很大关系。

⑧RIN((54)脚):模拟的红基色信号输入。

⑨GIN((48)脚):模拟的绿基色信号输入。

⑩BiN((43)脚);模拟的蓝基色信号输入。

以上三项为模拟的R、G、B三基色信号输入端。三路高阻输入端口独立工作,输入信号可调范围为0.5V(峰一峰值)~1.0V(峰一峰值),同时应加入输入嵌位电路,在信号取样前,应保证黑色电平相同,以免产生取样、量化误差。

(11)HSYNC((30)脚):行同步信号输入,此引出脚接收一个逻辑信号,用于建立行基准信号,并为图像取样时钟信号发生器提供基准频率,其逻辑属性由串行寄存器OEH的第6位控制(行同步极性标志位)。当行同步脉冲前沿为上升沿(正极性),则后沿时间可以忽略。

当行同步极性标志位为“0”时,行同步取下降沿(负极性);当行同步极性标志位为“l”时,行同步取上升沿(正极性)。行同步输入还包括噪波抑制施密特触发器,其输入极限电压为1.5V(峰一峰值)。

⑩VSYNC((31)脚):场同步信号输入脚。

⑩SOGIN((49)脚):带复合同步信号的绿基色信号输入,该输入脚内可以完成同步分离,即从绿基色信号中分离出复合同步信号,同步分离电路由一个带阈值的高速电压比较电路完成,阈值大小可以由程序控制,以10mV(峰一峰值)为步长,从输入信号最低电平10mV(峰一峰值)上升到300mV(峰一峰值)(即同步信息部分),输入信号与阈值150mV(峰一峰值)的高速比较电路进行幅度比较,小于阈值的信号有输出,大于阈值的信号无输出,它相当于一个幅度切割电路,从带有复合同步信号的绿基色信号中,提取复合同步信号。

(14)CLAMP((38)脚):外部钳位脉冲输入脚。钳位脉冲的作用是通过钳位电路,使R、G、B三路基色信号在信号取样、量化之前行与行之间基准黑电平保持一致,减小取样、量化误差,避免图像信号直流成分变动引起的信号动态范围扩大。

(15)COAST((29)脚):复合同步信号输入,进入集成电路内同步信号处理电路,完成行、场同步信号分离,分别输出行、场同步信号。

(16)REFBYBASS((58)脚):内部1.5V基准电压分压电路,它必须通过0.1uF的电容去耦,1.5V内部基准电压的精确度为4.0%,温度稳定性为50×10-6/℃,这对于MST9883集成电路内的大部分电压的应用已足够精确、稳定。如需要更高的精度,可以由外部电源提供基准电压。

(17)MIDSCV((37)脚):内部中间电压基准去耦,它必须通过0.1uF电容去耦,用来减小电源噪波和寄生效应。

(18)FILT((33)脚):滤波器的外部电路,它能保证时钟信号的正确产生,滤波元件参数选择的精度和稳定性直接影响数据信号的精确性与稳定性。

(19)AVDD:主电源3.3V电压,它能为MST9883集成电路内的主要模拟电路提供电源电压,电源电压必须稳定,并经外部滤波电路去耦。

(20)VDD:数字信号处理电路供电电源。由于高速数字信号处理电路(基准频率高达110MHz)容易对电源电路产生干扰,为了降低这种干扰,通常数字信号处理电路的供电电路与模拟信号处理电路供电电源分开供电,这就可以减小数字电路对模拟电路的干扰。

如果该处理电路要求使用较低的逻辑电平,则VDD还可以连接2.5V的供电电压。

(20)PVLO((26)、(27)、(34)、(35)脚):时钟信号发生器供电电路,它是MST9883集成电路最敏感的电路,一般也采用单独供电的办法,以免与其他电路产生串扰。

(22)GND:集成电路接地点,为了防止电路之间通过地电阻造成寄生干扰,因此MST9883集成电路采用大面积接地的办法,减小地电阻影响。

五、MST9883在TCL液晶电视中的实测引脚电压值

|

类型 |

符号 |

功能说明 |

电压值 |

引脚 |

|

输入 |

RAIN GAIN BAIN HSYNC VSYNC SOGIN CLAMP COAST |

R模拟转换输入 G模拟转换输入 B模拟转换输入 行同步输入 场同步输入 G信号复合同步输入 钳位输入(外部钳位信号) PLL 控制输入 |

0.0 V to 1.0 V 0.0 V to 1.0 V 0.0 V to 1.0 V 3.3 V CMOS 3.3 V CMOS 0.0 V to 1.0 V 3.3 V CMOS 3.3 V CMOS |

54 48 43 30 31 49 38 29 |

|

输出 |

Red [7:0] Green [7:0] Blue [7:0] DATACK HSOUT VSOUT SOGOUT |

R转换输出 G转换输出 B转换输出 数据时钟输出 行同步输出 场同步输出 G信号复合同步输出 |

3.3 V CMOS 3.3 V CMOS 3.3 V CMOS 3.3 V CMOS 3.3 V CMOS 3.3 V CMOS 3.3 V CMOS |

70–77 2–9 12–19 67 66 64 65 |

|

参考 |

REF BYPASS MIDSCV FILT |

内部参考电压旁路 内部中点电压旁路 PLL环路滤波 |

1.25 V |

58 37 33 |

|

供电 |

VD

VDD

PVD GND |

模拟部分供电

数字输出部分供电

PLL部分供电 接地 |

3.3 V

3.3 V

3.3 V 0 V |

39, 42, 45, 46, 51, 52, 59, 62 11, 22, 23, 69, 78, 79 26, 27, 34, 35 1, 10, 20, 21, 24, 25, 28, 32, 36, 40, 41, 44, 47, 50, 53, 60, 61, 63, 68, 80 |

|

控制 |

SDA SCL A0 |

I2C总线数据线 I2C总线时钟线 I2C接口地址输入 |

3.3 V CMOS 3.3 V CMOS 3.3 V CMOS |

57 56 55 |

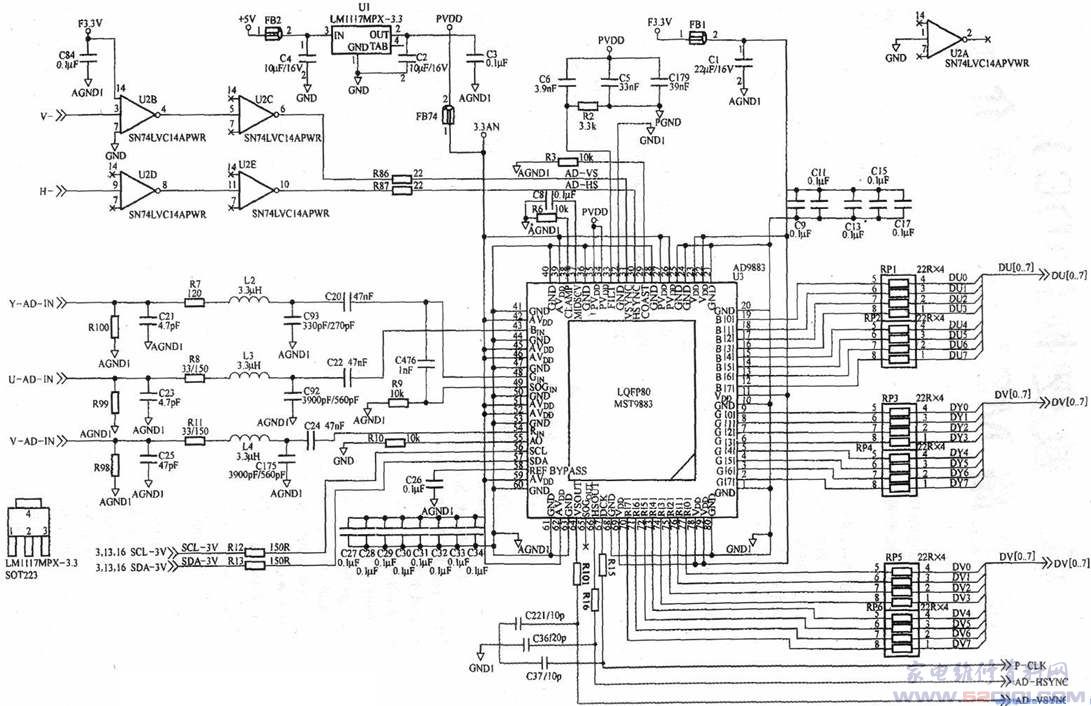

六、MST9883典型应用电路

下面就利用上图来简述MST9883集成电路的信号流程。

图像信号数字化处理电路的主要功能是把输入的图像信号经过钳位、采样、量化后,形成PDP显示屏驱动电路需要的数字信号。

经过前级图像信号处理后的亮度信号Y(或G基色信号)、色差信号U(或B基色信号)、色差信号V(或B基色信号),经外接RC耦合电路后,分别输入到MST9883的(48)、(43)、(54)脚。行、场同步信号HYNC、VYNC经两级放大、整形后,加到MST9883集成电路的(30)和(31)脚。I2C总线的时钟信号SCL和数据信号SDA,被外接三极管经电平转换后,通过RC耦合电路,加到模/数变换集成电路MST9883的(56)、(57)脚,对模/数变换集成电路实现控制、设置。

模/数变换集成电路(MST9883)在I2C总线控制下,对R、G、B三基色信号或Y、U、V色差信号进行取样、量化,完成模/数变换,使模拟的图像信号变为数字化的图像信号。8比特数字化的图像信号,从MST9883集成电路的输出端并行输出。其中(77)~(70)脚输出RO-R7基色数字信号或DVO~DV7色差数字信号,(9)~(2)脚输出GO~G7基色数字信号或DYO~DY7亮度数字信号,(19)~(12)脚输出BO~B7基色数字信号或DUO~DU7色差数字信号。

模/数变换集成电路MST9883内的时钟信号受行同步信号控制,保证每行图像信号的采样相位一致。

模/数变换集成电路内形成的时钟信号以MST9883集成电路的(67)脚输出,行、场同步信号从(66)脚、(64)脚输出,分别经RC滤波电路后,送到后级图像信号处理集成电路,保证系统内各集成电路时基相同,协调工作。

网友评论