概述:AN9600内部集成了系统时钟振荡器、8位高效DSP微处理器、8位MCU控制接口、I2C 设备序列传输接口、8MB只读语音存储器ROM、波表ROM(可提供128种音色和47种鼓声)、8KB静态读写内存SRAM、RC基频振荡电路、数字倍频控制PLL电路、2级混音滤波运算放大器、电源稳压器和小功率音频放大器等电路单元于一体。AN9600系列可存储语音时长为20~340s,还有680s、1360s长时间OTP语音微处理器。AN9600系列内建2×16位数/模转换、256阶语音合成音量调整、可程序化控制音频输出单声道/立体声切换、可程序化控制DAC输出模式(分时/合成/位准调整)、可程序化MCU传输接口、可程序化控制内部波形处理的取样频率、可外挂闪存任意扩展存储容量,以及设智能录放音功能;可播放8~128通道电脑网络音乐;可输出单声道或立体声音频信号直推扬声器;可外接驱动LED数码管/LCD液晶显示屏或LED发光二极管等。工作电压范围2.5~4.5V;省电模式和唤醒特性以减少功耗,静止耗电电流约为2μA。

一、AN9600引脚和封装

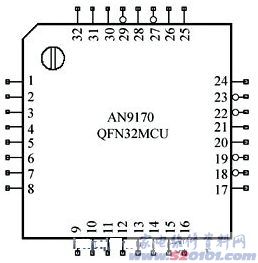

封装形式有SDIP28P、QFN32P、QFP44P、LQFP48P等。如AN9170的QFN32P封装的引脚排列如下图所示。

二、MCU模式1.系统初始化

系统上电后,将进行一连串的初始值设定,此时系统处于“忙”状态,无法接收任何数据。当初始值设定完成后,迅速清除“忙”状态,进入等待接收数据状态,且系统会进入省电模式(DAC、EQ-OP、AMP、CLOCk皆为休眠状态)。这时可通过各种命令对系统进行功能及状态设定操作,以达到主系统所需求的功能。

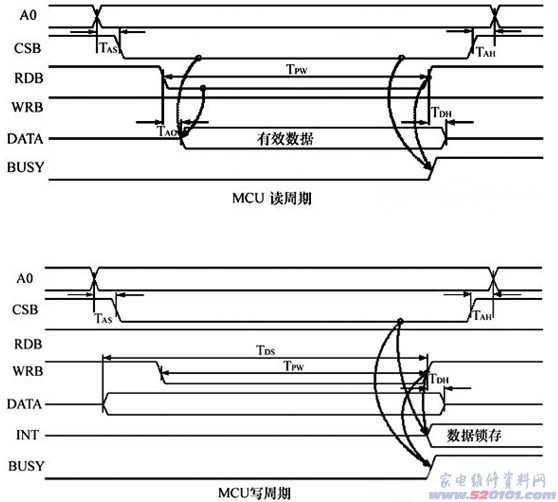

2. 系统读取/写入操作:对系统作写入操作时,CSB及WRB引脚端必须置为“0”,此时不参考RDB的信号准位。因此RDB信号连接与否取决于MCU的控制信号,若MCU未提供RDB信号时,建议将RDB信号连接至GND或CSB引脚端。

当需要对系统执行写入操作时(不论是命令信号或是数据信号),必须在系统不是处于“忙”状态时执行。 当对系统完成写入操作后,系统会马上反应为“忙”,直到系统可继续接收新的数据或者相对应的程序处理完毕时,系统才会自动解除 “忙”状态。

读取系统的“忙”状态时,MCU D[1:0]相对反映出MCU传输模式的数据传输要求(IRQ)或“忙”状态(Busy)。

D[0] “忙”状态置“0”=系统目前可接收新的作业处理;置“1”=系统目前无法处理新的作业。

D[1] IRQ的状态置“0”=系统目前没有MIDI数据的要求;置“1”=系统目前需要新的MIDI数据。此位反映出系统是否需要新的MIDI数据作处理。系统中共有32字节的缓冲空间,当剩余的缓冲空间小于或等于所设定的字节大小(初始值为15,可通过命令 = MCU_IRQ_BYTE _SIZE更改设定值)时,此位D[1]会为”1”且脚位信号IRQB会反映出所设定的电平值(可通过命令= MCU_IRQ_高电平或低电平更改设定值)。当有新的MIDI数据被写入缓冲空间后,D[1] 位会为”0”且脚位信号IRQB会被释放。表2为控制功能描述。

MCU接口控制时序:下图所示是MCU读周期时序图。图5所示是MCU写周期时序图。

三、I2C模式

系统上电后将进行一系列初始化设定,初始化过程中不接收任何数据传输。系统对于I2C的地址处理能力仅支持7位寻址。I2C总线上的数据传输速率并无最低限制,最高可达4Mb以上。I2C的传输规格在此不多作说明,仅描述传输封包的方向及系统字节的关系。图7是I2C模式的SDA和SCL信号完整传输关系。图7为“主”系统对“从”系统写入数据的传输封包及确认关系。图8为 “主”系统对“从”系统读取数据的传输封包及确认关系。图9为数据传输关系及含义的解释。

I2C的主控端分为硬件电路或软件仿真。当主控端为硬件电路时,则一切都不会有问题;当主控端为软件仿真时,需要注意以下几点:

SDA及SCL为“主”系统时,通过I/O所控制。I2C信号为低电平时,I/O输出低准位;I2C信号为高电平时,I/O必须设定为输入。因为“从”系统于确认后会将SCL设定为低电平后再进行内部运算,直到运算结束可再接收另外的数据时,才会将信号释放,在此过程中,“主”系统必须监测信号是否为高电平,若不为高电平时,则必须等到信号为高电平后才可继续执行传输操作。“主”系统必须全程监测SCL为高电平状态时,才可在传输正确情况下将传输速率提高。“主”系统读取SDA的数据必须在SCL准位为高电平期间,因为在SCL为高电平的时候,SDA由低电平变为高电平时为停止工作,由高电平变低电平是启动控制,这两种状况都是由“主”系统产生的。

网友评论