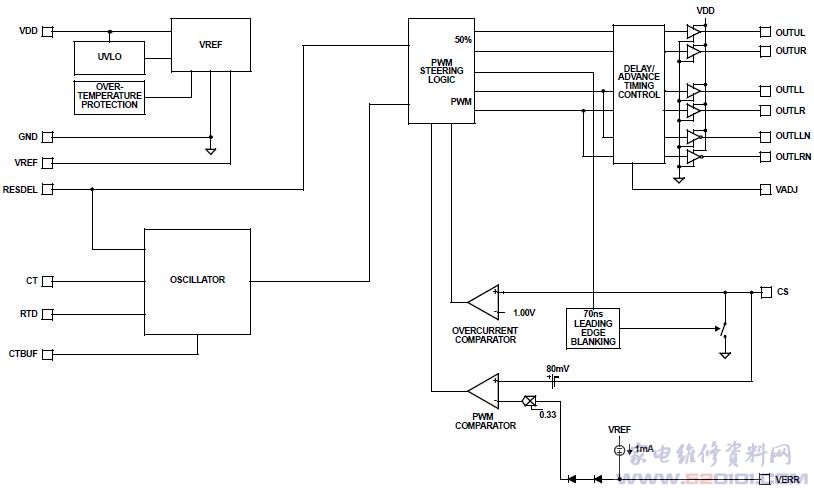

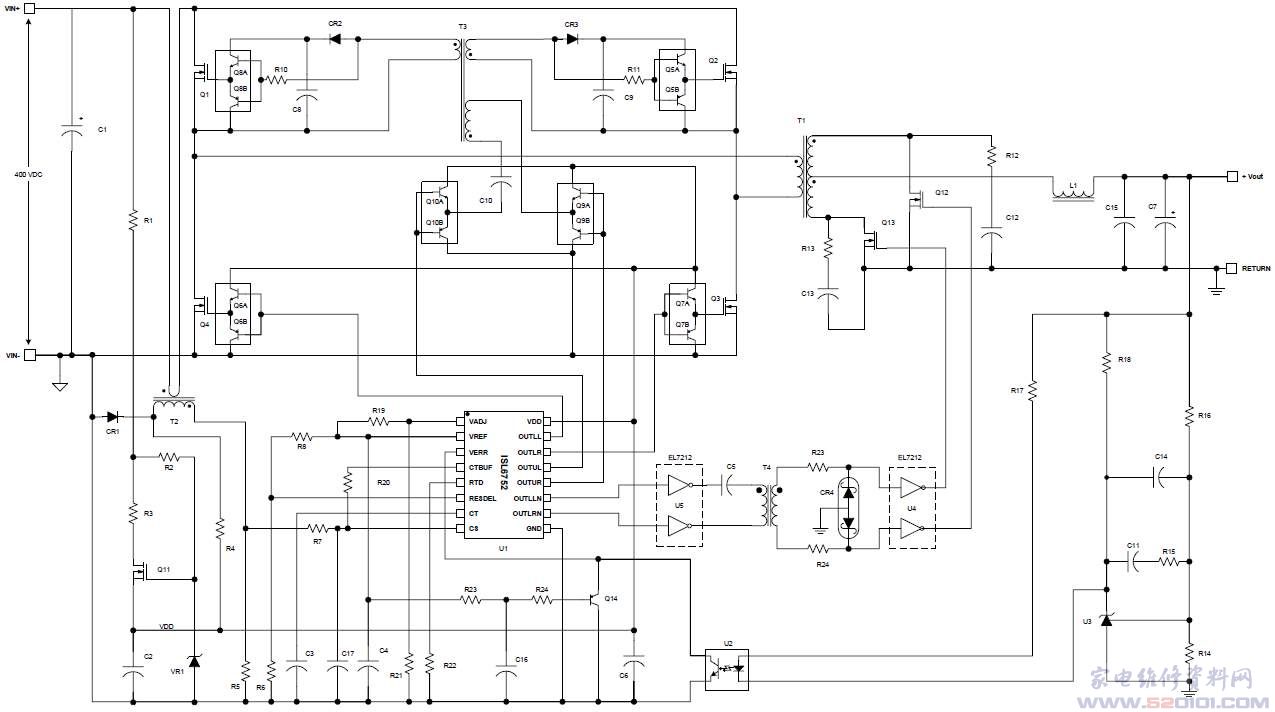

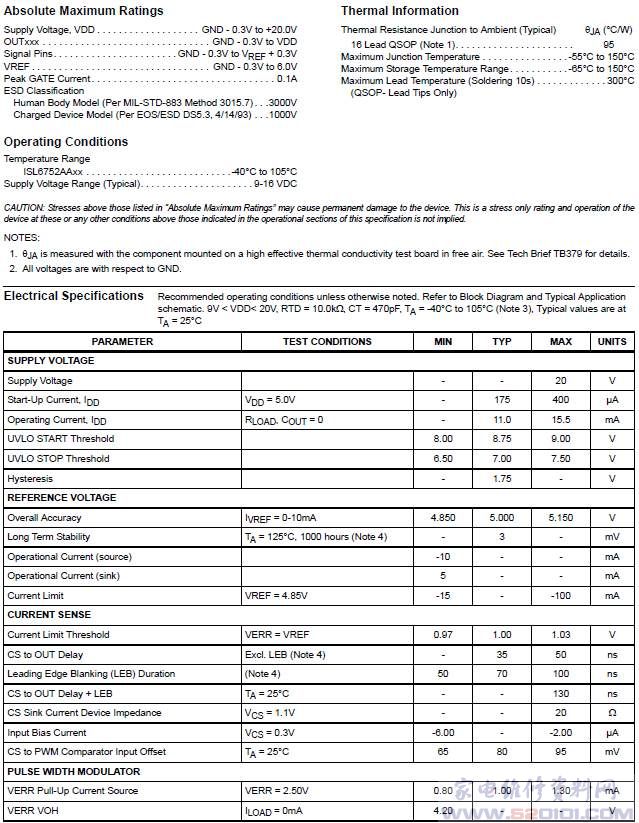

概述:该ISL6752是INTERSIL公司生产的一款高性能,低引脚数的替代零电压开关(ZVS)全桥PWM控制器。像Intersil的ISL6551,它实现ZVS操作,通过驱动上桥的FET在一个固定的50%占空比,而下桥FET的后沿调制的可调谐振开关延迟。相比,更熟悉的移相控制方法,该算法提供了相当于提高效率,改进过电流和更低的低引脚数封装的复杂性轻载性能。

该ISL6752功能互补PWM输出,用于同步整流(SR)控制。该补充的输出可以被动态地提前或延迟相对于使用外部控制voltage.This PWM输出先进的BiCMOS工艺设计,具有精度死区时间和共振延迟控制,以及振荡器可调节到2MHz工作频率。此外,多脉冲抑制确保交替输出脉冲可能出现脉冲跳跃低的占空比。

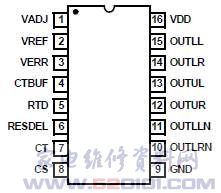

一、ISL6752引脚功能

引脚中文说明:

VDD:控制器的电源输入端,要优化抗扰度,需用一个陶瓷电容尽可能靠近并挎接在VDD与GND引脚。

GND:器件上所有功能和电源地都以这个引脚为基准。由于峰值电流及高频特点,低阻抗布局非常必要,高度推荐使用接地面及短线迹。

VREF:5.00V的基准电压输出端,有3%的容差遍及输入、负载及温度变化范围。可连接0.1uF至2.2uF的低ESR电容至GND以作滤波这输出所需。

CT:振荡器的定时电容可以挎接在这个引脚与GND之间。这个电 容是用200uA的内部电流源来充电,其放电是通过可调的RTD设置的电流源。

RTD:这是振荡器的定时电容的放电电流制引脚。挎接在这引脚和GND的电阻的电流决定CT放电电流的大小。 CT放电电流通常是电阻电流的20倍。PWM的死区时间是由定时电容的放电时间来决定的。在RTD引脚的标称电压是2.00V。

CS:过流比较器的输入端,过流比较器的标称临近值设置在1.00V。

OUTLL或OUTLR任意一端被终止,CS引脚与GND引脚将被短路,直至下一个周期开始。

VERR:加到PWM比较器反相输入端的控制电压。对于闭环电压调节,外部误差信号放大器的输出电压可以直接加在这个输入端,也可以通过光藕合器。VERR具有额定值为1mA上拉电流源。

CTBUF:是CT引脚上的锯齿振荡波型的缓冲输出端,能够提供2mA的电流。这个引脚的对地偏移电压是0.4V,并且谷峰标称增益为2,这可以用来做斜率补偿。

OUTUL/OUTUR:这两各输出端是用来控制上端FETs在固定的50%工作周期以交替运行。其死区时间由RTD调节。

OUTLL/OUTLR:这两各输出端是用来控制下端FETs ,其脉宽可调,工作在交替状态,其控制范围最高可以与上端FETs一样宽。

RESDEL:设置上下FETs之间的开启与关断谐振延迟周期,加在此端上的电压决定了上端FET关断相对于下端FET开启的相对时间,把控制电压从0V增加到2V会使谐振延迟时间从0%增加到100%的死区时间,控制电压除以2代表死区时间的百分比是等于谐振延迟时间。在实际应用中,为了确保下端FETs 在最大占空比时是优先关断(比上端FETs ),最大的谐振延迟必须小于2V。

OUTLLN/OUTLRN:这两各输出端与PWM(下端)FETs成互补, OUTLLN与/OUTLL成互补,OUTLRN/OUTLR成互补。是用于控制二次侧同步整流上FETs的控制,其间的相位关系由加在VADJ的电压控制。

VADJ:这个引脚上0~5V的电压是用来设置OUTLLN相对于OUTLL、OUTLRN相对于OUTLR的相位超前与滞后时间。

2.425V以下的电压,OUTLLN/OUTLRN的相位超前于 OUTLL/OUTLR。

2.575V以上的电压,OUTLLN/OUTLRN的相位滞后于 OUTLL/OUTLR。

2.5+/-0.75V之间的电压,OUTLLN/OUTLRN的相位与 OUTLL/OUTLR的相位相同。

相位超前与滞后的范围是0ns或者40~300ns之间,随着与2.5V电压差的增加,超前与滞后的相位差也会增大。控制电压与相位差的关系是非线性的,当控制电压接近2.5V时,电压增益(△t/△v)是很小的,并且会随着电压接近控制极限而很快地增大。

二、ISL6752功能和特性

• ZVS 运行可调共振延迟

• 延迟/前置可调的同步整流控制输出

• 电流摸式控制

• 3%限流临界

• 可调死区时间控制

• 175μA 启动电流

• 输入电源欠压切断保护

• 可调振荡频率高达2MHz

• 内部过温保护

• 缓冲振荡锯齿输出

• 快电流传感延迟

• 可调周期性峰值限流电流

• 70ns 上升沿消隐

• 多脉冲抑制

• 不含铅 (RoHS Compliant)

• ELV, WEEE, and RoHS Compliant

网友评论