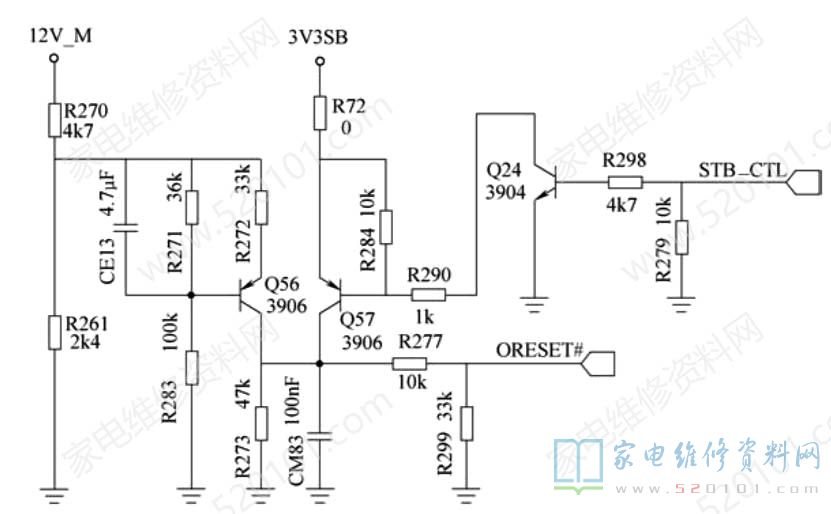

液晶电视主板复位电路如图1所示,开机瞬间,12V_M供电经R270,因CE13两端的电压不能突变,Q56截止,同时,主芯片IO端口U1_I(HI3751)的AD4脚输出的STB_CTL为低电平,此时Q24截止,Q57截止,复位端ORESET#为低电平,CPU复位;电容CE13经过一段时间充电后,两端电压差使Q56导通,CPU复位端U1_I(HI3751)的AD2脚ORESET#变为高电平,复位结束。

待机瞬间,CE13两端的电压不能突变,Q56导通,同时,主芯片IO端口输出的STB_CTL为高电平,此时Q24导通,Q57导通,CPU复位端ORESET#被拉高,不复位。

网友评论