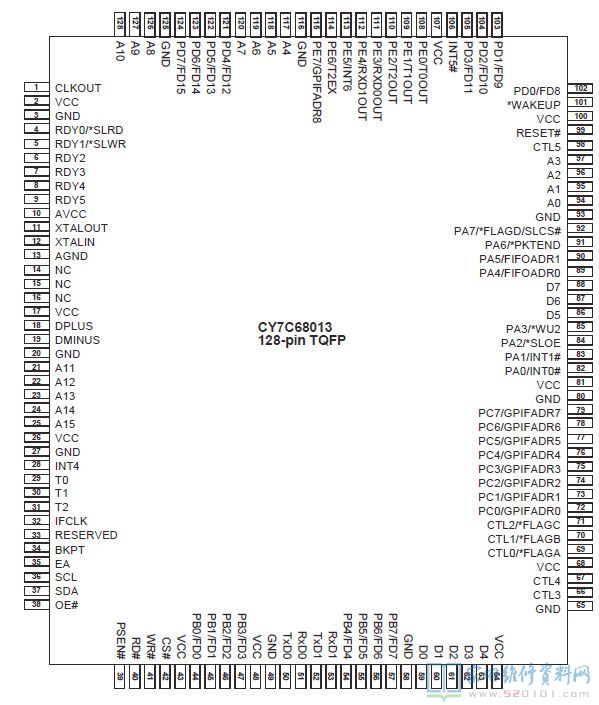

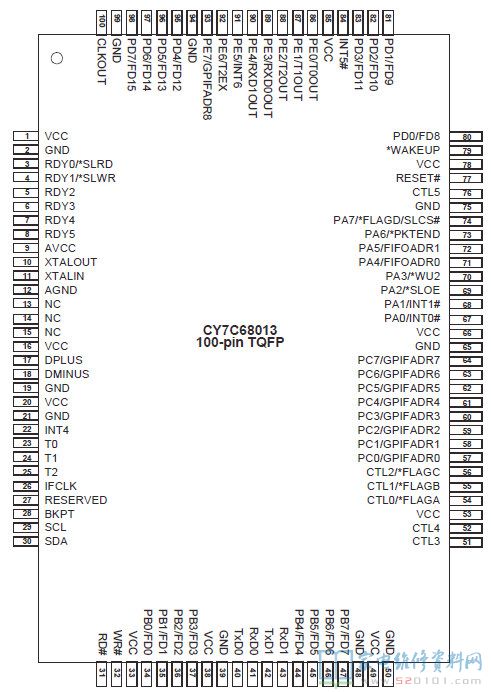

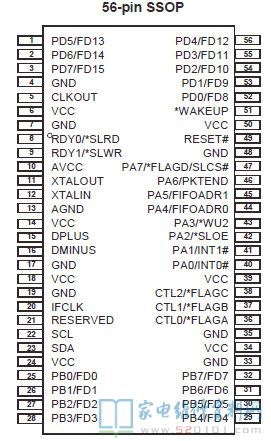

CY7C68013芯片中集成了一个GPIF模块,让用户可以按照外设的时序进行波形编辑,而不需要复杂的程序描述,就可以保证GPIF与内部,FIFO的协调工作,实现芯片与高速外围设备之间的逻辑连接和高速数据传输。CY7C68013采用128(128-PINTQFP)脚、100(100-pinTQFP)脚、56(56-pinQFP)脚封装工艺。

一、CY7C68013功能和特性

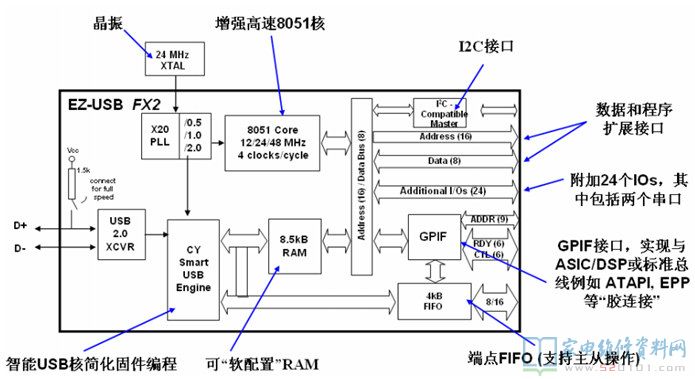

1、支持USB2.0,内部包括USB2.0收发器、串行接口引擎(SIE)以及增强型51内核;

2、灵活配置,可“软配置”RAM,取代了传统51的RAM和ROM,程序可以通过以下方式下载:通过USB口下载;通过外部E2PROM装载;外界存储设备(仅128引脚支持)

3、模式灵活,可设置为主从模式,主模式下可对外部FIFO、存储器、ATAn接口设备进行高速读写操作,从模式下外部主控器(例如DSP、MCU)可把GPIF端口当作FIFO进行高速读写操作。

4、支持与外设通过并行8位或者16位总线传输。

二、CY7C68013引脚功能

三、CY7C68013内部方框图

四、CY7C68013硬件连接方式

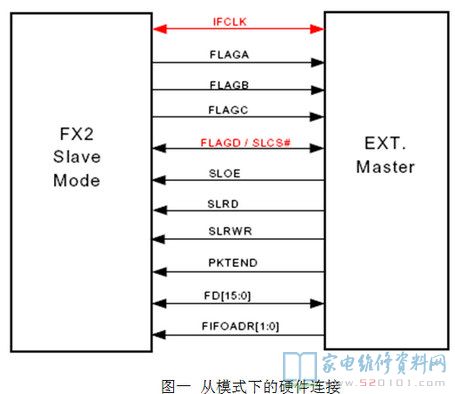

在Slave FIFO方式下,外部逻辑与FX2的连接信号图如下:

IFCLK:FX2输出的时钟,可做为通讯的同步时钟;

FLAGA,FLAGB,FLAGC,FLAGD:FX2输出的FIFO状态信息,如满,空等;

SLCS:FIFO的片选信号,外部逻辑控制,当SLCS输出高时,不可进行数据传输;

SLOE:FIFO输出使能,外部逻辑控制,当SLOE无效时,数据线不输出有效数据;

SLRD:FIFO读信号,外部逻辑控制,同步读时,FIFO指针在SLRD有效时的每个IFCLK的上升沿递增,异步读时,FIFO读指针在SLRD的每个有效—无效的跳变沿时递增;

SLWR:FIFO写信号,外部逻辑控制,同步写时,在SLWR有效时的每个IFCLK的上升沿时数据被写入,FIFO指针递增,异步写时,在SLWR的每个有效—无效的跳变沿时数据被写入,FIFO写指针递增;

PKTEND:包结束信号,外部逻辑控制,在正常情况下,外部逻辑向FX2的FIFO中写数,当写入FIFO端点的字节数等于FX2固件设定的包大小时,数据将自动被打成一包进行传输,但有时外部逻辑可能需要传输一个字节数小于FX2固件设定的包大小的包,这时,它只需在写入一定数目的字节后,声明此信号,此时FX2硬件不管外部逻辑写入了多少字节,都自动将之打成一包进行传输;

FD[15:0]:数据线;

FIFOADR[1:0]:选择四个FIFO端点的地址线,外部逻辑控制。

其他更多关于CY7C68013相关资料,请点击下载:CY7C68013.doc

网友评论