概述:EDE111-6AB是ELPIDA半导体生产的一款存储芯片。

一、EDE111-6AB引脚功能

1.CK,/CK是不同的差分时钟输入。所有的地址和控制输入信号的采样在交叉点上的

正面边缘的CK和消极边缘/CK。输出(读取)数据是参考交叉点CK和/CK的。(两个方向的交叉)。

2./CS(输入引脚)。所有的控制被遮罩当/CS是高电平时,/CS提供外部行选择在系统是多行时。/CS被认作是部分的控制代码。

3./RAS,/CAS,/WE(输入引脚)。/RAS,/CAS和/WE(除/CS外)确定命令正在进入。

4.A0到A13(输入引脚)。提供行地址为主动命令和列地址和自动预位的读/写命令来选择一个位置输出内存阵列在各自的行中。地址输入也提供运算代码在模式寄存器设置命令期间。

5.A10(AP)(输入引脚)。A10被预采样在预加压命令期间去决定是否预加压提供一行(A10=低)或所有行(A10=高)。如果仅仅一行被加压,这行将被选择通过BA0,BA1和BA2。

6.BA0,BA1,BA2(输入引脚)。BA0,BA1和BA2确定哪一行是主动的,读,写或者预加压命令正在被应用。BA0和BA1也决定是否模式寄存器或扩充模式寄存器访问在MRS或EMRS(1),EMRS(2)周期。

7.CKE(输入引脚)。CKE高触发,低禁止,内部时钟信号和设备输入缓冲器和输出驱动器。CKE低时提供预断电和自刷新操作,或者主动断电。它是同步的断电进入和退出,也是同步的自刷进入与退出。它必须保持高通量的读写访问。输入缓冲器,除了CK,/CK,CKE被禁止在断电期间,输入缓冲器,除了CKE被禁止在自刷新。

8. DM、UDM和LDM(输入引脚)DM是一个信号输入掩码写入数据。输入数据是蒙面取样时,一致认为高投入数据在写入权限。DM取样在DQS两个边缘。尽管DM仅仅是输入引脚,DM的装载可以和DQ、DQS相匹配。

*8构造,DM功能禁止,当RDQS功能通过EMRS进入时。

*16构造,UDM控制高字节(DQ8 到DQ15)和LDM控制低字节(DQ0到DQ7)。在这个数据表中,DM代表UDM和LDM。

9. DQ(输入/输出引脚)。双向的数据总线。

10. DQS、/DQS、UDQS、/UDQS、LDQS、/LDQS(输入/输出引脚)。输出读数据,输入写数据为资源同步操作。边读取数据,集中在写入数据。用于获取写入数据,/DQS被禁止通过EMRS。 *16构造,UDQS、/UDQS控制高字节(DQ8到DQ15)和LDQS、/LDQS控制低字节(DQ0到DQ7).在这个数据表中,DQS代表UDQS和LDQS,/DQS代表/UDQS和/LDQS。

11. RDQS、/RDQS(输出引脚)。差分数据选通只为读操作。DM和RDQS功能是能够转换通过EMRS。这些引脚存在仅仅是*8构造。/RDQS输出禁止当/DQS禁止通过EMRS。ODT(输入引脚)。ODT(双终端控制)寄存高信号,是终端抵抗内部的DDR2内存。当激活时,ODT仅仅应用在DQ、DQS、/DQS、RDQS、/RDQS和DM信号上*8构造。*16构造,ODT应用在DQ、UDQS、/UDQS、LDQS、/LDQS和UDM、LDM信号上。ODT引脚被忽略如果扩充模式寄存器(EMRS)编程使能ODT时。任何时间EMRS可以使能ODT功能。ODT不能驱动高直到八个时钟后EMRS已启用。

12. VDD、VSS、VDDQ、VSSQ(电源电压)。VDD和VSS为内部电路的电源电压引脚,VDDQ和VSSQ为输出缓冲器的电源电压引脚。

13. VDDL和VSSDL(电源电压)。VDDL和VSSDL是DLL电路的电源电压引脚。

14. VREF(电源电压)。SSTL_18参考电压:(0.50+/-0.01)*VDDQ

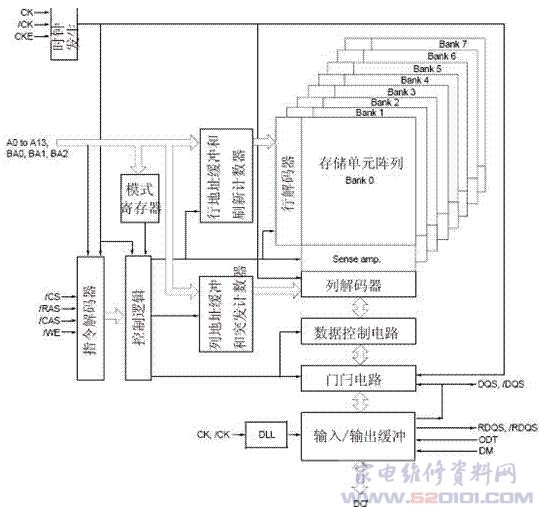

二、EDE111-6AB功能说明

1. 密度:1Gbits

2. 结构 16M words × 8 bits × 8 banks (EDE1108AEBG)

8M words × 16 bits × 8 banks (EDE1116AEBG)

3. 封装 60-ball FBGA (EDE1108AEBG)

84-ball FBGA (EDE1116AEBG)

Lead-free (RoHS compliant) and Halogen-free

4. 电源电压:VDD, VDDQ = 1.8V ± 0.1V

5. 数据比率:800Mbps/667Mbps(最大)

6. 1KB页面大小(EDE1108AEBG)

行地址:A0到A13

列地址:A0到A9

7. 2KB页面大小(EDE1116AEBG)

行地址:A0到A12

列地址:A0到A9

8. 八个内部banks为并列操作

9. 接口:SSTL_18

10. 脉冲时间:(BL):4,8

11. 脉冲字节(BT):次序(4,8)

交错(4,8)

12. /CAS Latency (CL): 3, 4, 5, 6

13. 预充电:自动预充电选项为每个突发访问

14. 驱动力量:正常和弱

15. 恢复:自动恢复,自我恢复

16. 恢复周期:8192cycles/64ms

平均恢复周期:

7.8us 0℃<=TC<=+85℃

3.9us +85℃<TC<=+95℃

17. 工作温度范围:

TC=0℃到+95℃

三、EDE111-6AB特性与特点

1.双数据比率结构;每个时钟周期两个数据传输。

2.高速数据传输,实现了由4位预取流水线架构

3.双向差分数据选通(DQS,/DQS)传输/接收数据的采集数据通过接收器

4.DQS是边对齐数据读取,中心对齐数据写入

5.差分时钟输入(CK,/CK)

6.DLL aligns DQ and DQS transitions with CK transitions

7. 控制进入每个正的CK边缘;数据和数据遮罩参照这两个边缘的DQS

8. 数据遮罩(DM)为写入数据

9. 发布/CAS通过可编程添加剂潜伏期为更好的控制和数据总线的效率

10. 片外驱动阻抗调整以及对模终止为更好的信号质量

11. Programmable RDQS, /RDQS output for making × 8 organization compatible to × 4 organization

12. /DQS,(/RDQS)能够被禁用单端数据选操作。

网友评论