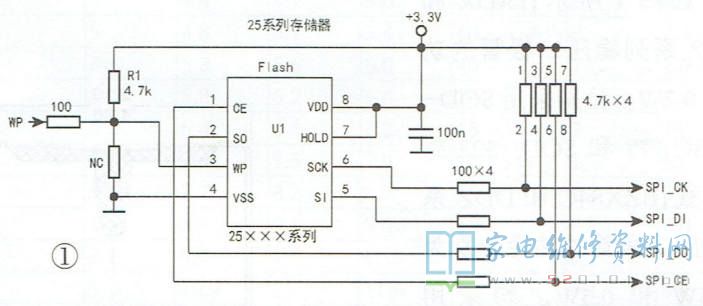

在液晶电视中,Flash存储器多采用8脚贴片封装的25xx系列,如PS25LV020、PM25VF040、MX25L1605等,其引脚功能见表1。25xxx系列Flash存储器的典型应用电路如图1所示,U1的片选操作端①脚(CE,低电平有效)受CPU输出的SPL CE信号控制,U1的串行数据输出端①脚(SO)接CPU的SPI DO端,U1的写操作端③脚(WP, 低电平有效)受CPU输出的WP_ FSH信号控制,U1的数据输入端⑤脚(SI )接CPU的SPIL DI端,U1的时钟信号输入端⑥脚(SCK),接CPU的SPI_ CK端。U1的⑦脚(HOLD)为中断控制端,正常时该脚为高电平(约3.3V),若为低电平时,Flash将中断与CPU的通讯;U1的⑧脚(VDD)为供电端,供电电压在2.7V~3.6V之间。

U1的写保护端③脚(WP )既接上拉电阻R1,又连接到主芯片的WP端。此脚的电平受软件控制,当为高电平时,执行WRSR(写状态寄存器)指令;当为低电平时,与BPL(块保护锁定)寄存器共同决定写入状态。U1的⑦脚(HOLD )接3.3V,即让该脚一直为高电平,表示不启用暂停控制功能。U5的⑥脚为串行时钟输入端,在待机状态,该端信号频率为14MHz;在开机状态,该端信号频率为36MHz。实际检修时,可依此判断Flash的工作频率是否正确。

网友评论