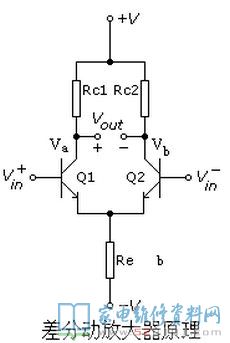

差分放大器也叫差动放大器是一种将两个输入端电压的差以一固定增益放大的电子放大器,有时简称为“差放”。差分放大器通常被用作功率放大器(简称“功放”)和发射极耦合逻辑电路 (ECL, Emitter Coupled Logic) 的输入级。如果Q1 Q2的特性很相似,则Va,Vb将同样变化。例如,Va变化+1V,Vb也变化+1V,因为输出电压VOUT=Va-Vb=0V,即Va的变化与Vb的变化相互抵消。这就是差动放大器可以作直流信号放大的原因。

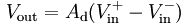

若差放的两个输入为 ,则它的输出Vout为:

,则它的输出Vout为:

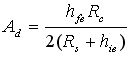

其中Ad是差模增益 (differential-mode gain),Ac是共模增益 (common-mode gain)。

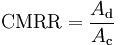

因此为了提高信/噪比,应提高差动放大倍数,降低共模放大倍数。二者之比称做共模仰制比(CMRR, common-mode rejection ratio)。共模放大倍数AC可用下式求出:

Ac=2Rl/2Re

通常以差模增益和共模增益的比值共模抑制比 (CMRR, common-mode rejection ratio) 衡量差分放大器消除共模信号的能力:

由上式可知,当共模增益Ac→0时,CMRR→∞。Re越大,Ac就越低,因此共模抑制比也就越大。因此对于完全对称的差分放大器来说,其Ac = 0,故输出电压可以表示为:

所谓共模放大倍数,就是Va,Vb输入相同信号时的放大倍数。如果共模放大倍数为0,则输入噪声对输出没有影响。

要减小共模放大倍数,加大RE就行通常使用内阻大的恒流电路来带替RE

差分放大器是普通的单端输入放大器的一种推广,只要将差放的一个输入端接地,即可得到单端输入的放大器。很多系统在差分放大器的一个输入端输入反馈信号,另一个输入端输入反馈信号,从而实现负反馈。常用于电机或者伺服电机控制,稳压电源,测量仪器以及信号放大。在离散电子学中,实现差分放大器的一个常用手段是差动放大,见于多数运算放大器集成电路中的差分电路。

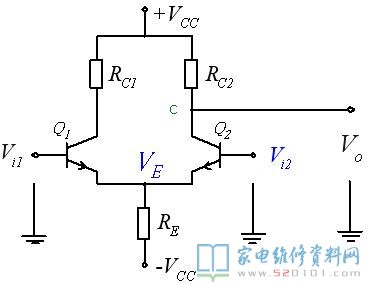

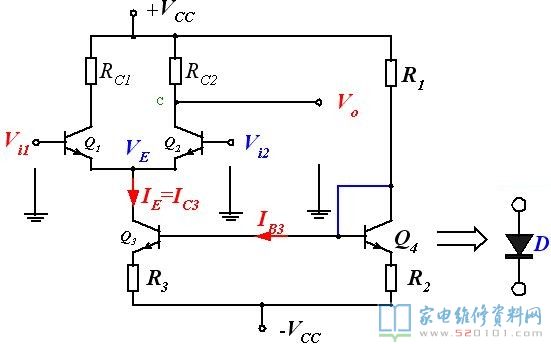

单端输出的差动放大电路 (不平衡输出)

单端较差动输出之幅度小一倍,使用单端输出时,共模讯号不能被抑制,因Vi1与Vi2同时增加,VC1与VC2则减少,而且VC1=VC2,但Vo =VC2,并非于零(产生零点漂移)。

但是加大RE阻值可以增大负回输而抑制输出,并且抑制共模讯号,因Vi1=Vi2时, Ii1及Ii2也同时增加,IE亦上升而令VE升高,这对Q1和Q2产生负回输, 令Q1和Q2之增益减少,即Vo减少。

当差动讯号输入时,Vi1 = -Vi2,IC1增加而IC2减少,总电流IE = IC1 + IC2便不变, 因此VE也不变,加大RE电阻值之电路会将差动讯号放大,不会对Q1及Q2产生负回输

及抑制。

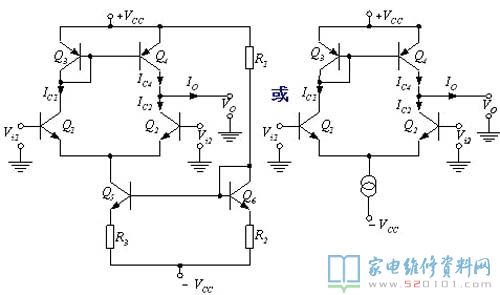

a)提高增益:

。

。 b)减低功率消耗(相对纯电阻来说)。

c)提高差动放大之输出电压。

d)提高共模抑制比CMRR。

设Vi1增加,则Vi2减少(但数量相等,Vi1 = Vi2)

即差动输入,则IC1升而IC2下降(并且,ΔIC1 = ΔIC2)

因电流镜像原理,IC4 = IC1

故此,Io = IC4 IC2 = IC1 IC2 (ΔIo = 2ΔIC1或2ΔIC2)

这说明了输出电流是IC1和IC2的相差,即将输出变为具有双端差动输出性能的单端输出 (故对共模讯号之抑制有改善因双端差动输出才能产生消除共模讯号作用)。

IC2减少使Q2之VCE增加,使Vo上升而IC4增加,使Q4之VCE减少,这也是使Vo增加, 故此,Vo上升之幅度是使用电阻为负载之单端输出电压大一倍。

网友评论