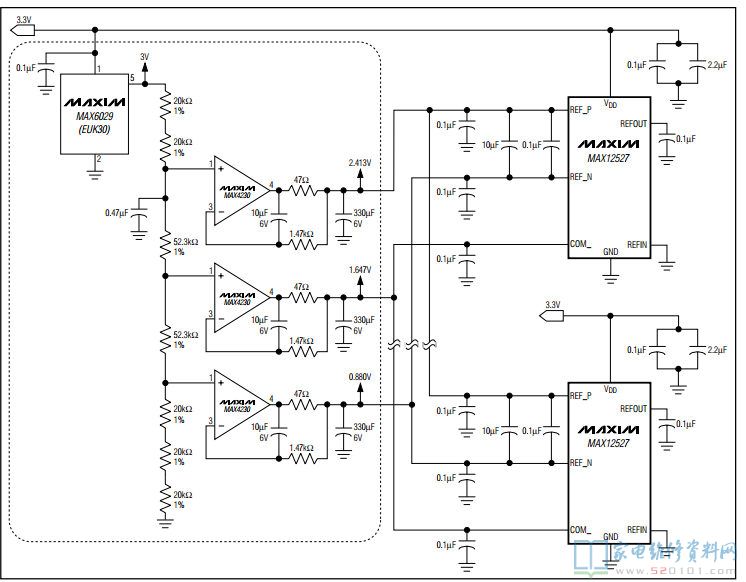

MAX12527采用灵活的基准结构,可以使用内部2.048V带隙基准或外部基准,并允许两个ADC共用基准。基准结构使得满量程模拟输入可以在±0.35V至±1.15V范围内调整。MAX12527提供共模基准,简化了设计,并减少了差分模拟输入电路的外部元件数量。支持单端或差分输入时钟。用户可选择的二分频(DIV2)与四分频(DIV4)模式,可以实现灵活的设计,并有助于消除时钟抖动的负面影响。较宽的时钟占空比变化可以由ADC内部占空比均衡器(DCE)补偿。

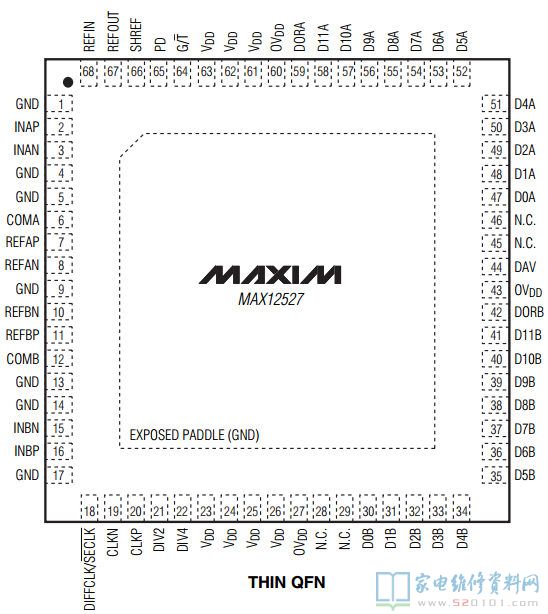

MAX12527具有两个并行、12位宽、CMOS兼容的输出端口。数字输出格式可以通过引脚选择为2的补码或格雷码。用于数字输出级的独立电源输入可接受1.7V至3.6V电压,便于与不同逻辑电平接口。MAX12527采用10mm x 10mm x 0.8mm、68引脚、带裸露焊盘(EP)的薄型QFN封装,工作在扩展级温度范围(-40°C至+85°C)。

一、MAX12527功能和特性

高达400MHz的直接IF采样

优异的动态性能

fIN = 70MHz/175MHz时,SNR为70.4dB/69.8dB

fIN = 70MHz/175MHz时,SFDR为84.4dBc/80.2dBc

3.3V低功耗工作

647mW (差分时钟模式)

620mW (单端时钟模式)

完全差分或单端模拟输入

可调的差分模拟输入电压

750MHz输入带宽

可调的内部或外部基准,基准可共用

差分或单端时钟

接收25%至75%的时钟占空比

用户可选择的DIV2与DIV4时钟模式

断电模式

2的补码或格雷码格式的CMOS输出

超量程与数据有效指示

小尺寸、68引脚、薄型QFN封装

提供14位兼容版本(MAX12557)

可提供评估板(请定购MAX12557EVKIT)

二、MAX12527引脚功能

三、MAX12527内部方框图

网友评论